Letter pubs.acs.org/journal/apchd5

# **Electrically Tunable High-Quality Factor Silicon Microring Resonator** Gated by High Mobility Conductive Oxide

Wei-Che Hsu, Cheng Zhen, and Alan X. Wang\*

Cite This: ACS Photonics 2021, 8, 1933-1936

**ACCESS**

Metrics & More

Article Recommendations

ABSTRACT: Silicon microring resonators play pivotal roles in photonic integration circuits due to the advantages of low power consumption, high bandwidth, and ultracompact size. However, silicon microring resonators also face great challenges to control the working wavelength due to fabrication errors and temperature variation. In this work, we demonstrate an electrically tunable silicon microring resonator driven by a titanium-doped indium oxide/hafnium oxide/silicon metal-oxide-semiconductor capaci-

tor, achieving a high electro-optic tuning efficiency of 130 pm/V with a high quality factor between 11900 and 4700. The high electro-optic tuning efficiency can be used to compensate for the drift of resonance wavelength induced by temperature fluctuation up to 12 K with an extremely low power consumption of 11 pW/nm, which is superior to the conventional thermal tuning.

KEYWORDS: silicon photonics, microring resonator, transparent conductive oxides, electrical tuning, energy-efficient photonic device

icroring resonators (MRRs) can serve as multipurpose photonic devices for laser emission, electro-optic (E-O) modulation, add-drop filtering, wavelength conversion, and wavelength division multiplexing (WDM)/demultiplexing. Therefore, MRR is one of the most critical devices in photonic integrated circuits with exclusive advantages in terms of high energy efficiency, wide bandwidth, and a small footprint for optical communication and optical computing.<sup>1,4</sup> In silicon photonics, silicon MRR (Si MRR) is often used as a tunable optical filter and an E-O modulator by applying electronic signals.5 Most reported Si MRRs are driven by reversed PN junctions, which only provide a low E-O tuning efficiency below 40 pm/V. 5-9 However, the resonance wavelength of the Si MRR is easily affected by fabrication errors and fluctuations in temperature due to the high thermo-optic (T-O) coefficient of silicon  $(1.86 \times 10^{-4} \text{ K}^{-1})^{10}$  while the reversed PN junction structure cannot sufficiently compensate the drift. Therefore, a thermal heater is widely used to control the resonance wavelength of Si MRR with the sacrifice of high power consumption (in mW/nm) and the requirement of controlling circuits. 11-13 Recently, metal-oxide-semiconductor (MOS) Si MRR with heterogeneously integrated materials such as III-V, poly-Si, and transparent conductive oxides (TCOs), have been reported with much higher E-O tuning efficiency. 14-16 Of these heterogeneous gate materials, TCOs offer a large plasma dispersion effect and can be easily integrated with silicon photonics by DC- or RF-sputtering. 17,18 For example, our group experimentally demonstrated an indium-tin-oxide (ITO)-gated Si MRR, which achieved an ultrahigh E-O tuning efficiency of 271 pm/V using a narrow microring waveguide with a hafnium oxide (HfO<sub>2</sub>) insulator. 19 However, the quality factor (Q-factor) is limited to 1000 due to the high optical loss from the ITO gate. In principle, the optical loss can be reduced

by high-mobility TCO materials to improve the Q-factor of the electrically tunable MRR.<sup>20</sup> Titanium-doped indium oxide (ITiO) is one of the high-mobility TCO materials, which can achieve the high mobility of 105 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> by an optimized RF sputtering process.<sup>2</sup>

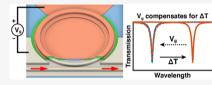

In this Letter, we demonstrate an electrically tunable Si MRR with an integrated ITiO/HfO<sub>2</sub>/Si MOS capacitor, which has a high E-O tuning efficiency of 130 pm/V with a high Qfactor between 11900 and 4700. The high E-O tuning efficiency can be used to compensate for the temperature fluctuation ( $\Delta T$ ) up to 12 K with an extremely low power consumption of 11 pW/nm. Figure 1a shows the threedimensional (3D) schematic of the electrically tunable MRR with a radius of 6  $\mu$ m. The ITiO-gated MOS MRR is fabricated on a Si-on-insulator (SOI) substrate with the fabrication flow described in our previous work.<sup>22,23</sup> In contrast to our earlier work, <sup>23</sup> the SiO<sub>2</sub> layer of the MOS capacitor is replaced by a 10 nm HfO<sub>2</sub> to enhance the E-O tuning efficiency. 19 Besides, the thickness of the ITiO gate is reduced to 8 nm to suppress the optical absorption, which covers the active region, as shown in Figure 1b. Figure 1c shows the cross-sectional schematic in the device's active region and the accumulation layers. The Drude model can describe the optical properties of ITiO,<sup>24</sup> and the fundamental device working principle has been discussed in more detail in our previously published work. 19,23 When a

Received: April 20, 2021 Published: July 7, 2021

ACS Photonics pubs.acs.org/journal/apchd5 Letter

**Figure 1.** (a) 3D schematic of the ITiO-gated Si MOS MRR. (b) An optical image of the fabricated MRR. The ITiO gate is highlighted by the dashed line and covers the active region of the MRR except the coupling region to the bus waveguide. (c) The cross-sectional schematic and the example of optical mode profile ( $|E|^2$ ) at  $V_{\rm g}=-3$  V in the active region. The negative  $V_{\rm g}$  induces carrier accumulation and refractive index modulation.

negative bias  $(V_{\rm g})$  is applied, electrons accumulate in the ITiO layer, which causes the refractive index to change in the accumulation layer. Similarly, the refractive index change in the Si accumulation layer is induced by the holes accumulated with the negative  $V_{\rm g}$ . The resonance wavelength of the MRR has a blue shift due to the changes of refractive indices in ITiO and Si accumulation layers.

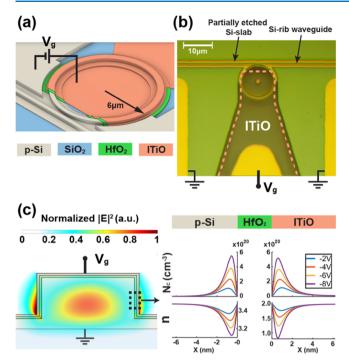

Figure 2a shows the transmission spectra of the tunable MRR versus the gate voltage  $V_{\rm g}$  at room temperature. When a negative  $V_{\rm g}$  is applied to the ITiO gate, the resonance wavelength experiences a blue shift. The initial tunable MRR  $(V_g = 0 \text{ V})$  is designed at the overcoupling condition, so the extinction ratio (ER) increases until  $V_{\rm g}$  goes to -4 V. The  $\Delta\lambda$ and Q-factor at each  $V_{\rm g}$  are measured and plotted in Figure 2b. The  $\Delta \lambda$  is almost linearly proportional to the  $V_{\rm g}$  from  $-2~{\rm V}$  to −6 V, and it has a high average E-O tuning efficiency of 130 pm/V. When the negative  $V_{\rm g}$  increases, it induces higher optical absorption loss and causes the Q-factor to degrade gradually from 11900 to 4700. Since the Q-factor depends on the loss of the MRR, it can be used to derive the loss of the optical waveguide in ITiO-gated MRR. The dashed line in Figure 2c is obtained from the passive Si MRR and it shows that the waveguide bending loss of the MRR is 0.34 dB/mm based on a Q-factor of 13000. Additionally, the blue curve shows the total loss of the ITiO-gated MRR waveguide, including both the bending loss and optical absorption. It increases from 1.03 to 12.3 dB/mm due to the increased optical absorption as  $V_{\sigma}$  rises.

The thermal effect of the MRR is measured by increasing the substrate temperature, which is controlled by a temperature controller (Thorlabs-TED200C) with a TEC element

Figure 2. (a) Normalized transmission spectra of the ITiO-gated MOS Si MRR with different  $V_{\rm g}$  values. (b) Experimentally measured Q-factor (blue line, left y-axis) and  $\Delta\lambda$  (red line, right y-axis). (c) Blue curve: the loss in ITiO-gated MOS Si MRR, including both waveguide bending and optical absorption losses. Dashed line: the bending loss of the intrinsic Si MRR extracted from the passive Si MRR with a Q-factor of 13000. (d) Experimental  $\Delta\lambda$  caused by  $\Delta T$  without gate voltage ( $V_{\rm g}=0$  V).

(Thorlabs-TEC J6), and it has a T-O tuning efficiency of 86 pm/K, as shown in Figure 2d. The plasma dispersion effect induced by the gate voltage can be used to compensate for the T-O effect. The solid lines in Figure 3a show that the resonance wavelength has a red shift when we increase the substrate temperature. With negative gate voltages,  $V_{\rm g}$ , the resonance wavelength is blue-shifted against the red-shift induced by  $\Delta T$ , as shown in the dashed lines of Figure 3a, resulting in stabilized working wavelength even as the temperature varies. The inset of Figure 3a plots the required  $V_{\sigma}$  to compensate for  $\Delta T_{\tau}$  and the thermal tuning range of this MRR is around 12 K. Since the plasma dispersion effect of ITiO is accompanied by the increase of optical absorption, using the gate voltage to compensate the temperature drift will simultaneously induce variations of ER and Q-factor, which are plotted in Figure 3b. The ER of the MRR can increase after the compensation due to the overcoupling condition of the initial MRR ( $V_{\sigma} = 0$  V). Besides, it can almost have the same ER as the initial MRR ( $V_g = 0 \text{ V}, \Delta T = 0 \text{ K}$ ) when it compensates for 12 K temperature drift. The Q-factor is gradually decreasing because of the incremental optical absorption loss.

ACS Photonics pubs.acs.org/journal/apchd5 Letter

Figure 3. (a) Normalized transmission spectra of ITiO-gated MOS Si MRR with different  $\Delta T$  and compensated  $V_{\rm g}$ . The solid lines are the spectra red-shifted by  $\Delta T$ . The dashed lines are the spectra relying on  $V_{\rm g}$  to compensate for the  $\Delta T$ . Inset: the required  $V_{\rm g}$  to compensate for  $\Delta \lambda$  caused by  $\Delta T$ . (b) After the compensation by applying  $V_{\rm g}$ , and the change of Q-factor (blue line, left y-axis) and ER (red line, right y-axis).

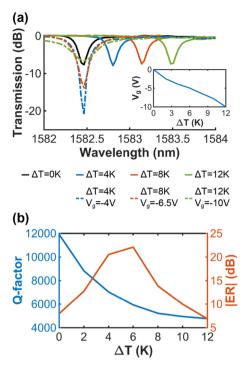

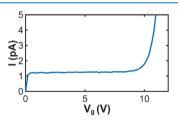

We measured the leakage current of the ITiO/HfO<sub>2</sub>/Si MOS capacitor and plotted it in Figure 4. It has an average

Figure 4. Leakage current of ITiO/HfO $_{\rm 2}/{\rm Si}$  MOS capacitor as a function of  $V_{\rm g}$

leakage current of 1.2 pA and an average E-O tuning efficiency of 105 pm/V at  $V_{\rm g}$  from 0 to -10 V. It has a tuning power efficiency of 11 pW/nm, which is much more efficient than thermal tuning in the range of several mW/nm. From Figure 4 we also see this tunable MRR has a breakdown voltage of around -10 V. Therefore, we can have an adequate electrical tuning range from 0 to -10 V, and it can compensate for  $\Delta T$  up to 12 K with low power consumption. However, we still need to further enhance the E-O tuning efficiency to compensate for  $\Delta T$  up to 20 K, which is the suggested temperature tuning range for silicon photonics to be used in on-chip optical communication. By narrowing the MRR's waveguide to 300 nm, as discussed in our previous work, we can achieve higher E-O tuning efficiency, and it potentially can compensate  $\Delta T$  up to 30 K.

In conclusion, we demonstrated an electrically tunable ITiOgated MOS Si MRR. It achieved a high E-O tuning efficiency of 130 pm/V with a high Q-factor of 11900. This tunable MRR can be used to compensate the temperature drift up to 12 K while still maintaining a high Q-factor above 4700. In addition, it has a high power efficiency of 11 pW/nm, which is much more efficient than the conventional thermal tuning of several mW/nm. With a narrower waveguide width of MRR, we expect it to offset the  $\Delta T$  up to 30 K. Therefore, the tunable ITiO-gated MOS Si MRR can provide high energy efficiency for on-chip WDM communication on a silicon photonics platform.

#### AUTHOR INFORMATION

## **Corresponding Author**

Alan X. Wang — School of Electrical Engineering and Computer Science, Oregon State University, Corvallis, Oregon 97331, United States; orcid.org/0000-0002-0553-498X; Email: wang@oregonstate.edu

#### **Authors**

Wei-Che Hsu — School of Electrical Engineering and Computer Science, Oregon State University, Corvallis, Oregon 97331, United States

Cheng Zhen — School of Electrical Engineering and Computer Science, Oregon State University, Corvallis, Oregon 97331, United States

Complete contact information is available at: https://pubs.acs.org/10.1021/acsphotonics.1c00600

#### Note:

The authors declare no competing financial interest.

### ACKNOWLEDGMENTS

We would like to thank the Materials Synthesis and Characterization Facility (MASC) and the Electronic Microscopy Facility in Oregon State University for supplying the resource for our device fabrication. We acknowledge the funding support provided by the AFOSR MURI Project FA9550-17-1-0071, the NSF GOALI Project 1927271, and the NASA ESI Program 80NSSC21K0230.

## REFERENCES

- (1) Bogaerts, W.; de Heyn, P.; van Vaerenbergh, T.; de Vos, K.; Kumar Selvaraja, S.; Claes, T.; Dumon, P.; Bienstman, P.; van Thourhout, D.; Baets, R. Silicon Microring Resonators. *Laser Photonics Rev.* **2012**, *6* (1), 47–73.

- (2) Longhi, S.; Feng, L. Unidirectional Lasing in Semiconductor Microring Lasers at an Exceptional Point [Invited]. *Photonics Res.* **2017**, *5* (6), B1.

- (3) Ying, Z.; Feng, C.; Zhao, Z.; Dhar, S.; Dalir, H.; Gu, J.; Cheng, Y.; Soref, R.; Pan, D. Z.; Chen, R. T. Electronic-Photonic Arithmetic Logic Unit for High-Speed Computing. *Nat. Commun.* **2020**, *11* (1), 1–9.

- (4) Xu, Q.; Schmidt, B.; Pradhan, S.; Lipson, M. Micrometre-Scale Silicon Electro-Optic Modulator. *Nature* **2005**, 435 (7040), 325–327.

- (5) Li, G.; Zheng, X.; Yao, J.; Thacker, H.; Shubin, I.; Luo, Y.; Raj, K.; Cunningham, J. E.; Krishnamoorthy, A. V. 25Gb/s 1V-Driving CMOS Ring Modulator with Integrated Thermal Tuning. *Opt. Express* **2011**, *19* (21), 20435.

- (6) Dong, P.; Liao, S.; Feng, D.; Liang, H.; Zheng, D.; Shafiiha, R.; Kung, C.-C.; Qian, W.; Li, G.; Zheng, X.; Krishnamoorthy, A. V.; Asghari, M. Low V\_pp, Ultralow-Energy, Compact, High-Speed Silicon Electro-Optic Modulator. *Opt. Express* **2009**, *17* (25), 22484.

- (7) Rosenberg, J. C.; Green, W. M. J.; Assefa, S.; Gill, D. M.; Barwicz, T.; Yang, M.; Shank, S. M.; Vlasov, Y. A. A 25 Gbps Silicon

ACS Photonics pubs.acs.org/journal/apchd5 Letter

- Microring Modulator Based on an Interleaved Junction. Opt. Express 2012, 20 (24), 26411.

- (8) Xiao, X.; Xu, H.; Li, X.; Hu, Y.; Xiong, K.; Li, Z.; Chu, T.; Yu, Y.; Yu, J. 25 Gbit/s Silicon Microring Modulator Based on Misalignment-Tolerant Interleaved PN Junctions. Opt. Express 2012, 20 (3), 2507.

- (9) Buckwalter, J. F.; Zheng, X.; Li, G.; Raj, K.; Krishnamoorthy, A. V. A Monolithic 25-Gb/s Transceiver with Photonic Ring Modulators and Ge Detectors in a 130-Nm CMOS SOI Process. *IEEE J. Solid-State Circuits* **2012**, 47 (6), 1309–1322.

- (10) Qiu, F.; Spring, A. M.; Miura, H.; Maeda, D.; Ozawa, M. A.; Odoi, K.; Yokoyama, S. Athermal Hybrid Silicon/Polymer Ring Resonator Electro-Optic Modulator. *ACS Photonics* **2016**, 3 (5), 780–783.

- (11) Dong, P.; Qian, W.; Liang, H.; Shafiiha, R.; Feng, N. N.; Feng, D.; Zheng, X.; Krishnamoorthy, A. V.; Asghari, M. Low Power and Compact Reconfigurable Silicon Multiplexing Devices. *Opt. Express* **2010**, *18* (10), 9852–9858.

- (12) Geng, M.; Jia, L.; Zhang, L.; Yang, L.; Chen, P.; Wang, T.; Liu, Y. Four-Channel Reconfigurable Optical Add-Drop Multiplexer Based on Photonic Wire Waveguide: Erratum. *Opt. Express* **2009**, *17* (20), 18209

- (13) Padmaraju, K.; Bergman, K. Resolving the Thermal Challenges for Silicon Microring Resonator Devices. *Nanophotonics* **2014**, 3 (4–5), 269–281.

- (14) Liang, D.; Kurczveil, G.; Fiorentino, M.; Srinivasan, S.; Bowers, J. E.; Beausoleil, R. G. A Tunable Hybrid III-V-on-Si MOS Microring Resonator with Negligible Tuning Power Consumption. 2016 Optical Fiber Communications Conference and Exhibition, OFC 2016, March 20–22, 2016, Anaheim, California, U.S.A., OSA Publishing, 2016; p Th1K.4.

- (15) Van Campenhout, J.; Pantouvaki, M.; Verheyen, P.; Selvaraja, S.; Lepage, G.; Yu, H.; Lee, W.; Wouters, J.; Goossens, D.; Moelants, M.; Bogaerts, W.; Absil, P. Low-Voltage, Low-Loss, Multi-Gb/s Silicon Micro-Ring Modulator Based on a MOS Capacitor. *Opt. InfoBase Conf. Pap.* **2012**, OM2E.4.

- (16) Swillam, M. A.; Zaki, A. O.; Kirah, K.; Shahada, L. A. On Chip Optical Modulator Using Epsilon-Near-Zero Hybrid Plasmonic Platform. Sci. Rep. 2019, 9 (1), 1–9.

- (17) Li, E.; Gao, Q.; Liverman, S.; Wang, A. X. One-Volt Silicon Photonic Crystal Nanocavity Modulator with Indium Oxide Gate. *Opt. Lett.* **2018**, 43 (18), 4429–4432.

- (18) Zhou, B.; Li, E.; Bo, Y.; Wang, A. X. High-Speed Plasmonic-Silicon Modulator Driven by Epsilon-Near-Zero Conductive Oxide. *J. Lightwave Technol.* **2020**, 38 (13), 3338–3345.

- (19) Li, E.; Nia, B. A.; Zhou, B.; Wang, A. X. Transparent Conductive Oxide-Gated Silicon Microring with Extreme Resonance Wavelength Tunability. *Photonics Res.* **2019**, *7* (4), 473–477.

- (20) Campione, S.; Wood, M. G.; Serkland, D. K.; Parameswaran, S.; Ihlefeld, J.; Luk, T. S.; Wendt, J. R.; Geib, K. M.; Keeler, G. A. Submicrometer Epsilon-Near-Zero Electroabsorption Modulators Enabled by High-Mobility Cadmium Oxide. *IEEE Photonics J.* **2017**, 9 (4), 1–7.

- (21) Hashimoto, R.; Abe, Y.; Nakada, T. High Mobility Titanium-Doped In203 Thin Films Prepared by Sputtering/Post-Annealing Technique. *Appl. Phys. Express* **2008**, *1* (1), 015002.

- (22) Hsu, W.-C.; Zhou, B.; Zhen, C.; Wang, A. X. Silicon Microring Resonator Driven by High-Mobility Conductive Oxide Capacitor. 2020 IEEE Photonics Conf. IPC 2020, Sept 28—Oct 1, 2020, Vancouver, BC, Canada, IEEE, 2020; p MF3.2.

- (23) Hsu, W.-C.; Li, E.; Zhou, B.; Wang, A. X. Characterization of Field-Effect Mobility at Optical Frequency by Microring Resonators. *Photonics Res.* **2021**, *9* (4), 615–621.

- (24) Liu, X.; Kang, J. H.; Yuan, H.; Park, J.; Cui, Y.; Hwang, H. Y.; Brongersma, M. L. Tuning of Plasmons in Transparent Conductive Oxides by Carrier Accumulation. *ACS Photonics* **2018**, *5* (4), 1493–1498.

- (25) Lee, H. W.; Papadakis, G.; Burgos, S. P.; Chander, K.; Kriesch, A.; Pala, R.; Peschel, U.; Atwater, H. A. Nanoscale Conducting Oxide PlasMOStor. *Nano Lett.* **2014**, *14* (11), 6463–6468.

- (26) Dong, P.; Liao, S.; Liang, H.; Shafiiha, R.; Feng, D.; Li, G.; Zheng, X.; Krishnamoorthy, A. V.; Asghari, M. Submilliwatt, Ultrafast and Broadband Electro-Optic Silicon Switches. *Opt. Express* **2010**, *18* (24), 25225.

- (27) Nitta, C.; Farrens, M.; Akella, V. Addressing System-Level Trimming Issues in on-Chip Nanophotonic Networks. *Proc. Int. Symp. High-Performance Comput. Archit.* **2011**, 122–131.

- (28) Joshi, A.; Batten, C.; Kwon, Y. J.; Beamer, S.; Shamim, I.; Asanović, K.; Stojanović, V. Silicon-Photonic Clos Networks for Global on-Chip Communication. *Proc.* 2009 3rd ACM/IEEE Int. Symp. Networks-on-Chip, NoCS 2009 2009, May, 124–133.